|

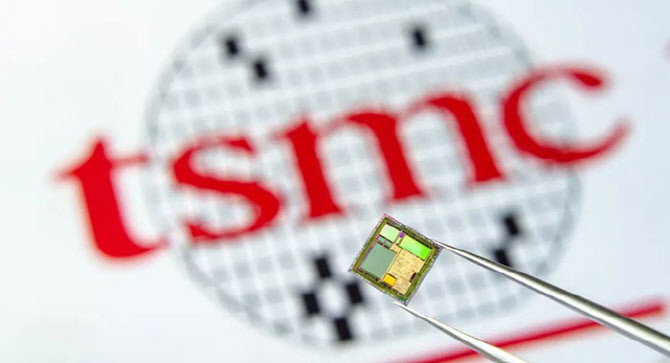

20일 헥서스 등 외신에 따르면 TSMC는 대만 국립 대학교(NTU)와 매사추세츠 공과 대학(MIT)과 함께 2차원(2D) 소재를 활용한 1나노 공정을 가능하게 하는 기술을 개발했다. 이 연구 결과는 과학 분야 국제학술지 ‘네이처’에 ‘반금속 및 단층 반도체 사이의 매우 낮은 접촉 저항’이라는 제목으로 지난 12일(현지시간)게재됐다.

연구 논문에 따르면 반도체의 핵심 재료인 실리콘을 반금속 원소인 비스무트(Bi)와 결합해 양자 한계에 가까운 낮은 저항을 달성할 수 있는 2D 소재로 대체했다. 과학자들은 2차원 소재가 실리콘의 물리적 한계를 대체할 가능성이 높다고 기대하고 있지만 2차원 소재의 고저항·저전류 등 문제를 극복하기 위해 애써왔다.

이번 논문 결과로 비스무트와의 결합으로 높은 접촉 저항과 낮은 전류 전달 능력이라는 고유한 특성을 가진 2차원 소재의 한계를 극복하고 반도체 효율을 최고 수준으로 높일 수 있다고 설명했다. 보도에 따르면 “이들은 공정 단위가 낮아질수록 실리콘 사용이 한계에 도달하는 것을 극복하기 위해 약 18개월동안 2차원 소재 연구 개발에 착수했다”며 “고저항·저전류의 2차원 소재 특성의 어려움을 이번 연구 결과를 통해 해결했다”고 말했다. 그러면서 이를 통해 ‘무어의 법칙’을 돌파할 수 있고 인공지능·전기차 등 사용과 1나노 이하 반도체 생산을 달성할 전망이라고 했다.

현재 초미세 공정 영역으로 평가받는 7나노 이하 반도체 양산이 가능한 업체는 전 세계에서 TSMC와 삼성전자뿐이다. 두 회사 모두 현재 5나노 제품을 양산하고 있다. 반도체는 나노 단위인 회로의 선폭이 좁을수록 저전력·고효율 칩을 만들 수 있어 초미세공정 경쟁이 치열하다.

반도체 업계에선 삼성전자와 TSMC 중 누가 먼저 3나노 양산을 시작하는지 주목하고 있었다. 3나노 공정으로 제작된 반도체는 5나노 대비 칩 면적은 35% 줄이면서, 성능과 배터리 효율은 각각 15%와 30% 올릴 수 있는 것으로 알려져 있다.

이에 TSMC는 현재 3나노 공정 양산에 박차를 가해 내년 말 양산에 돌입할 것으로 보인다. 최근에는 120억달러(약 14조원)를 투자해 미국 애리조나주 피닉스에 5나노 공정 생산 라인을 증설하고 있고 여기에 추가로 3나노 이하 최첨단 공정을 갖춘 생산 라인 5개를 증설해 총 6개의 신규 라인을 구축할 계획을 밝혔다.

삼성전자도 내년까지 3나노 양산에 돌입할 것이라고 밝힌 바 있다. 그러나 이번에 TSMC가 1나노 핵심 기술 개발에 다시 한번 성공하면서 삼성전자의 발등에 불이 떨어진 상황이다.

이종호 서울대 반도체공동연구소 소장은 “TSMC가 기술력과 자금력에서 경쟁사인 삼성전자보다 여전히 앞서고 있다는 것을 보여주기 위해 1나노 반도체 공정기술 개발이라는 상징적인 논문을 낸 것”이라며 “반도체 헤게모니(패권)겨루기 형식으로 보인다”고 말했다.

![월드컵까지 따냈다...스포츠산업 '생태계 파괴자' 된 빈살만[글로벌스트롱맨]](https://image.edaily.co.kr/images/Photo/files/NP/S/2023/11/PS23110500115t.jpg)

![[포토] 폭염 속 휴식취하는 건설 근로자](https://image.edaily.co.kr/images/Photo/files/NP/S/2023/08/PS23080100718t.jpg)

![[포토]최은우 '선두가 보인다'](https://spnimage.edaily.co.kr/images/Photo/files/NP/S/2024/04/PS24041900548t.jpg)

![[포토] 통합방위 발언하는 서강석 송파구청장](https://image.edaily.co.kr/images/Photo/files/NP/S/2024/04/PS24041900809t.jpg)

![[포토]청년도약계좌 22일부터 가입신청](https://image.edaily.co.kr/images/Photo/files/NP/S/2024/04/PS24041900757t.jpg)

![[포토] "의대 총장들 건의 수용한다"](https://image.edaily.co.kr/images/Photo/files/NP/S/2024/04/PS24041900703t.jpg)

![[포토] 학생들과 기념촬영하는 이재명](https://image.edaily.co.kr/images/Photo/files/NP/S/2024/04/PS24041900584t.jpg)

![[포토]김윤혜, 인형 그 자체](https://spnimage.edaily.co.kr/images/Photo/files/NP/S/2024/04/PS24041900148t.jpg)

![[포토] 고군택 '이번주 우승은 제가 하겠습니다'](https://spnimage.edaily.co.kr/images/Photo/files/NP/S/2024/04/PS24041900241t.jpg)

![[포토]유정복 인천시장 축사](https://image.edaily.co.kr/images/Photo/files/NP/S/2024/04/PS24041800929t.jpg)

!['더 뉴 아이오닉5'…"디자인·편의성·승차감 다 좋아졌네"[타봤어요]](https://image.edaily.co.kr/images/Photo/files/NP/S/2024/04/PS24041900771t.jpg)

![[포토]송민교 '버디를 노려본다'](https://spnimage.edaily.co.kr/images/Photo/files/NP/S/2024/04/PS24042000015t.jpg)